Overview

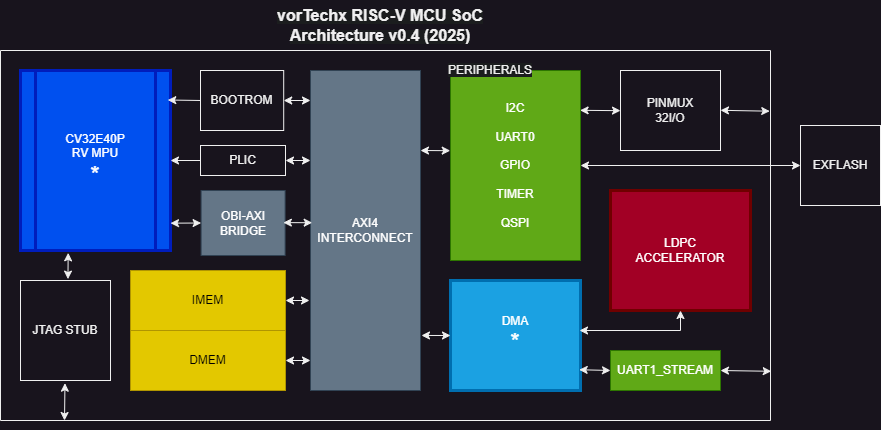

We architect microcontroller subsystems around RISC-V cores, focusing on clear bus fabrics (AXI-Lite), robust clock/reset strategy, and resource-aware RTL. Each design ships with timing reports, register maps, and bring-up notes so it’s portable across FPGA families and open PDKs.

Key Deliverables

- Synthesizable RTL

- Register maps & documentation

- Timing/resource reports

Example Diagram

Next Steps

Our current focus is to refine the SoC slice for tape-out readiness, with improved documentation and integration examples. Future updates will include benchmarking and live FPGA demos.